#### Introduction

The electrical appliances we use in our daily lives — from lights to computers — typically go through a shutdown process when they turn off. Power supplies require stable shutdown processes that can control for unexpected overshoot. In a stable shutdown process, the power supply smoothly drops the input voltage ( $V_{IN}$ ) to 0V.

For a stable shutdown, there should a steady  $V_{IN}$  drop, no negative output voltage ( $V_{OUT}$ ) overshoot, and no  $V_{IN}$  or  $V_{OUT}$  rebound. This article will discuss three unstable waveforms that can be observed during the power supply shutdown process. For the sake of this article, they will be designated as one of three classes: Class R (with a quick  $V_{IN}$  and  $V_{OUT}$  rebound), Class G (negative  $V_{OUT}$  overshoot), and Class B (with a delayed  $V_{IN}$  and  $V_{OUT}$  rebound).

### Class R Shutdown (Quick VIN and VOUT Rebound)

Figure 1 shows the Class R shutdown waveform. In a Class R shutdown, V<sub>IN</sub> steadily drops as the device shuts down, briefly increases during an energy spike, then begins to steadily drop again.

Figure 1: Class R Shutdown Waveform

There are two types of Class R waveforms, which are described below.

### Class R Shutdown (Type I)

A Class R Type I shutdown occurs when the DC/DC converter restarts.

Consider a standard shutdown. If  $V_{IN}$  drops to the chip's turn-off threshold, the chip shuts down.  $V_{OUT}$  drops during this process, causing the current to suddenly decrease. However, if the chip's input line has nowhere to release the excess energy from the inductive reactance during this process, then  $V_{IN}$  sharply increases.

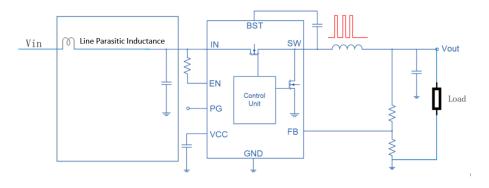

If  $V_{IN}$  exceeds the chip's operating threshold, the chip resumes operation and results in a nonmonotonous shutdown waveform. A Class R waveform is classified as Type I if there is a switch present on the SW side (see Figure 2).

Figure 2: Line Parasitic Inductance of Class R Type I Shutdown

The Class R Type I waveform is relatively simple to prevent. The chip's specifications provide the enable (EN) and  $V_{IN}$  under-voltage lockout (UVLO) parameters. Figure 3 shows the enable and UVLO specifications for the <u>MPM3683-7</u>, a <u>step-down power module</u>.

| Enable and Under-Voltage Lockout (UVLO)     |                         |                        |      |      |      |    |

|---------------------------------------------|-------------------------|------------------------|------|------|------|----|

| Enable input rising<br>threshold            | VIHEN                   |                        | 1.17 | 1.22 | 1.27 | V  |

| Enable hysteresis                           | Ven-Hys                 |                        |      | 200  |      | mV |

| Enable input current                        | IEN                     | $V_{EN} = 2V$          |      | 0    |      | μA |

| Soft shutdown discharge<br>MOSFET           | Ron_disch               |                        |      | 80   | 150  | Ω  |

| VIN UVLO                                    | -                       | -                      |      |      |      |    |

| VIN under-voltage lockout threshold rising  | VIN <sub>Vth_Rise</sub> | V <sub>CC</sub> = 3.3V | 2.1  | 2.4  | 2.7  | V  |

| VIN under-voltage lockout threshold falling | VIN∨th_Fall             |                        | 1.55 | 1.85 | 2.15 | V  |

Figure 3: MPM3683-7 Specifications

With these specifications in mind, there are two methods to avoid an unstable shutdown, described below:

- Reduce the V<sub>IN</sub> bounce by optimizing input filtering, reducing input inductance, selecting a capacitor with a larger capacitance and smaller equivalent series resistance (ESR) and equivalent series inductance (ESL), and placing the input capacitor as close to the IC as possible.

- 2. Select appropriate upper and lower voltage resistor dividers for EN, such that EN turns off when V<sub>IN</sub> drops to its UVLO threshold. This can prevent the IC from starting up again.

# Class R Shutdown (Type II)

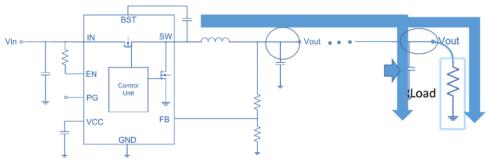

If the load is suddenly reduced, the excess energy stored in the integrated output inductor or the output line inductor cannot be released anywhere (see Figure 4). This can significantly increase  $V_{OUT}$  for a short time.

Figure 4: Class R Type II Event

To prevent a Class R Type II event, it is critical to optimize the output line. To optimize this line and reduce the chances of a rebound, reduce the line's inductive reactance and increase the capacitance at the load terminal.

### **Class G Waveform (Negative Overshoot)**

Figure 5 shows the Class G shutdown waveform. In a Class G shutdown, V<sub>OUT</sub> drops steadily, then drops rapidly past its target (called negative overshoot) before rising back up to its target value.

Figure 5: Class G Shutdown Waveform

Similar to Class R waveforms, Class G waveforms can be subdivided into two types.

# Class G Shutdown (Type I)

If the buck circuit's low-side MOSFET (LS-FET) does not turn off during shutdown, the inductor current continues to reverse. This situation is more common under no-load and light-loads conditions, and it can result in  $V_{OUT}$  dropping too low.

To prevent this issue, the DC/DC <u>converter</u> typically adds zero-current detection (ZCD) during shutdown, then automatically turns off the LS-FET when it detects that the current has reached 0A (commonly called the ZCD point) (see Figure 6). This approach can effectively prevent negative overshoot during shutdown.

Figure 6: Preventing Negative Overshoot in Class G Type I

# Class G Shutdown (Type II)

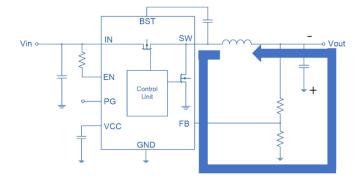

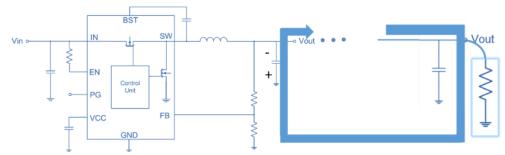

$V_{OUT}$  can experience negative overshoot due to the parasitic inductive reactance on the output line (see Figure 7). This type of shutdown is more likely to occur under heavy loads or during output short-circuit faults.

Figure 7: Reduce Parasitic Inductive Reactance of Class G Type II

The output line's inductive reactance must be minimized to prevent Class G Type II shutdown. In addition, the load terminal's capacitance should be increased.

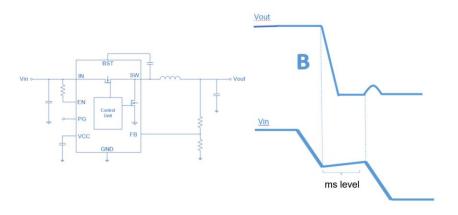

### Class B Waveform (Delayed VIN and VOUT Rebound)

Figure 8 shows a Class B shutdown waveform, which occurs under heavy loads. In a Class B waveform, both  $V_{IN}$  and  $V_{OUT}$  fall sharply, rise for a short period of time, then remain stable (as with  $V_{OUT}$ ) or fall again (as with  $V_{IN}$ ). Both scenarios are referred to as a rebound.

Figure 8: Class B Shutdown Waveform under Heavy Loads

Class B waveforms look similar to Class R waveforms, but Class R waveforms are due to the line inductance, and Class B waveforms have a much later rebound. After the first shutdown,  $V_{OUT}$  and  $V_{IN}$  typically rebound in microseconds with Class R shutdowns; however,  $V_{OUT}$  and  $V_{IN}$  may not rebound for up to tens of milliseconds in Class B shutdowns.

The dielectric absorption effect leads to the Class B waveform. If the input capacitor's discharge current is large then suddenly drops to 0A, the dielectric in the capacitor slowly releases some of the previously absorbed charges. Once the discharge current reaches the chip's start-up voltage again, V<sub>OUT</sub> rebounds.

To prevent a Class B shutdown, a chip can be powered off through EN, similar to the method used for Class R Type I shutdowns. Select the  $V_{IN}$  under-voltage protection (UVP) threshold and hysteresis to ensure that EN stays off. Then the  $V_{IN}$  rebound does not exceed the chip's power-on threshold and lead to an accidental restart. In addition, static loads can be added to consume any excess charge.

### Conclusion

This article explored three different types of shutdown waveforms (Class R, Class G, and Class B) related to the power supply shutdown process, with the intent of improving stability and preventing negative overshoot. These classes were also further subdivided, depending on the excess energy and loads conditions.

For more details, explore MPS's robust selection of step-down power modules.